# DEVELOPMENT OF MULTI-PURPOSE LOGIC MODULE USING FPGA

Ikuro Nagasawa#, Takatsugu Ishikawa, Hajime Shimizu, Kenichi Nanbu, Yoshinobu Shibasaki, Toshiya Muto, Ken Takahashi, Shigeru Kashiwagi, Fujio Hinode, Masayuki Kawai, Hiroyuki Hama

Research Center for Electron Photon Science, Tohoku University

Mikamine 1-2-1, Taihaku-ku, Sendai, Miyagi 982-0826, Japan

#### Abstract

We have developed a multi-purpose logic module with a field programmable gate array (FPGA) for a data acquisition system of an electromagnetic (em) calorimeter at Research Center for Electron Photon Science, Tohoku University. Construction of a new em calorimeter with 1,320 BGO crystals is planned to study the nucleon resonances via meson photo-production experiments. So far, this kind of nuclear physics experiments required a large space for the circuitry of handling trigger signals with many NIM modules, and the delay cables for analog signals from each crystal. We need to handle the huge number of digitized data under complicated trigger conditions. To handle the digital data efficiently and precisely, we have introduced the FPGA based module. FPGA is the logic device which a user can program in a field and it is reconfigurable. Because a development cost is low, and a development period is short, FPGA is suitable for a case having to renew frequently the logic depending on an experiment unlike an exclusive IC such as the Application Specific Integrated Circuit (ASIC). For these reasons, we developed the multi-purpose logic module equipped with high-speed FPGA. This module is equipped with Xilinx's FPGA Virtex-5 and can process signals at 450MHz. The problems in the data acquisition system are solved by the introduction of this module. We will report development status.

# FPGA を用いた多目的ロジックモジュールの開発

# 1. はじめに

電子光理学研究センターでは現在、BGO クリスタルを使用した次世代電磁カロリメータシステムを開発している。現在開発中のシステムは取り扱う信号数が 1600 チャネル以上と非常に多い。この信号数増加に対し既存のシステム構成のまま信号処理回路を増設すると、各検出器からの信号を処理する回路系の実装に必要な空間が著しく増加する。そのため信号処理における遅延の増加や、回路構成に必要な労力・時間の増大が懸念されている。

これらの問題に対処するためには、信号処理に使用するモジュールの集積度を飛躍的に向上させ、信号処理に使用するモジュール数を削減する必要がある。また、併せて信号処理回路が容易に再構成可能な構成となることも要求される。

以上の要件を満たすため Field Programmable Gate Array (FPGA)を搭載したモジュールが必要となった。過去にも電子光理学研究センターでは FPGA を搭載した汎用ロジックモジュールを開発しているが[1]、FPGA の性能やモジュールで扱える信号数が開発中のシステムの要件を満たさなかった。このため、新たに高性能 FPGA を搭載し、必要な数のデジタルI/O を有するモジュールを開発した。

高性能 FPGA の搭載により高集積度かつ大規模な信号処理回路の実装が可能となり、また回路の再構成が容易となった。新たに開発したモジュールは、最高動作周波数 450MHz の高速 FPGA、最大 2GSPS サンプリングが可能な高速フラッシュ型 A/D コンバータを搭載し、入力・出力共に各 128 チャネルのLVDS I/O を有し、上位計算機との通信のため

VMEbus インターフェースが実装されている。 VMEbus インターフェースや入出力各 128 チャネルの LVDS I/O を有するため、基板内の配線数は 7000本以上と著しく多くなったが、8 層基板を用いることで全配線パターンの結線と健全なシグナルインテグリティを達成した。

すでにモジュール自体は完成しており、各機能の動作確認も終了している。現在、運用に向け準備を行っている段階である。

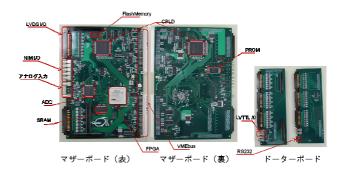

図1: 開発したモジュール (マザーボード1枚ドーターボード2 枚で構成される。ドーターボードでチャネル数を増やしている。)

# 2. 開発したモジュールの仕様と設計

#### 2.1 モジュールの仕様

開発したモジュールの設計仕様を表 1 に記載する。 本モジュールに搭載する FPGA は回路内で発生す る信号の遅延を最小化するため開発当時最も高速な Xilinx Virtex-5 ファミリの XC5VLX85-1FFG1153C を 選定した[2]。

また、今後の電磁カロリメータシステム開発に向け帯域幅 500 MHz、サンプリングレート 1GSPS 以上で動作するフラッシュ型 A/D コンバータを導入する必要があった。この A/D コンバータには National Semiconductor の ADC08D1020 を搭載した[3]。

実運用時には A/D コンバータに入力されるアナログ信号はシングルエンド信号である。しかし、ADC08D1020 にはシングルエンド信号ではなく差動信号を入力する必要がある。このため、シングルエンド信号を差動信号に変換する帯域幅 1500MHz のNational Semiconductor の差動アンプ LMH6552 をA/D コンバータ前段に配置した[4]。

ADC08D1020 は外部から入力されるクロックでサンプリングレートが定まる。必要に応じて柔軟にサンプリングレートを変更するため Texas Instruments のクロックジェネレータ CDCE421A を導入した[5]。CDCE421A は内部レジスタの書き換えによりクロックの逓倍率を変更でき、A/D コンバータのサンプリングレートを  $0.6 \sim 1.8 GSPS$  までの間で変更可能である。

また外部モジュールと本モジュール間でクロック 同期動作が可能となることが要求されたため、外部 クロック入力用の専用端子を設けた。

#### 2.2 モジュールの設計・実装

モジュールの開発にあたっては、システム開発の 要件を満たすためのシグナルインテグリティや今後 の研究活動の利便性向上を考えて設計を行った。設 計時に考慮した事項をいくつか紹介する。

#### 2.2.1 VMEbus インターフェース

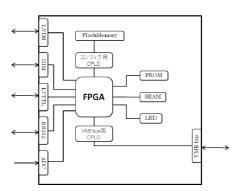

本モジュールでは上位計算機から VMEbus アクセスが可能となるように CPLD 上に VME スレーブモジュール機能[6]を実現する回路を実装した(図 2)。図 3 に本モジュールを利用する際に規定した VMEbus 上のデフォルト状態でのアドレス空間を示す。

# 2.2.2 リモートコンフィグレーション機能

上位計算機から遠隔でモジュール内 FPGA のコンフィグレーションの実行が可能となるようにコンフィグ用 CPLD を配置した(図 2)。

コンフィグ用 CPLD にはモジュール起動時または VMEbus からの命令で FlashMemory に書き込まれているデータを FPGA にダウンロードする回路が実装されている。加えて、コンフィグ用 CPLD にはウォッチドッグタイマーを用いた FPGA のハングアップ検出機能を備えており、ハングアップ検出時にはバックアップデータを用いて FPGA を再コン

### フィグレーションする。

表1: モジュールの設計仕様

| 表1: モシュールの設計仕様 |                      |

|----------------|----------------------|

| FPGA           | Xilinx Virtex-5 ファミリ |

|                | 型番:                  |

|                | XC5VLX85-1FFG1153C   |

|                | 最高動作周波数:450MHz       |

| アナログ入力         | 入力電圧:-2~2V           |

|                | 帯域幅:500MHz           |

|                | サンプリングレート:           |

|                | 0.5~1.8GSPS(可変)      |

|                | チャンネル数:2ch           |

|                | 分解能:8bit             |

| デジタル I/O       | LVDS I/O:入出力各 128ch  |

|                | NIM I/O:入出力各 3ch     |

|                | LVTTL I/O:入出力各 2ch   |

|                | 外部クロック入力(NIM):       |

|                | 1ch                  |

| VMEbus         | 有り                   |

| インターフェース       |                      |

| リモートリセット       | 有り                   |

| コンフィグレーション     | 1. JTAG ケーブル経由       |

| 手段             | 2. VMEbus 経由         |

|                | 3. PROM 経由           |

|                | 4. FlashMemory 経由    |

| SRAM 容量        | 16Mbit               |

| RS232 による通信    | デバッグ用                |

| 基板内クロック        | 30MHz                |

図 2: 開発したモジュールのブロック図(VMEbus 用 CPLD は VMEbus アクセスのために搭載している。また、コンフィグ用 CPLD の搭載によりリモートコンフィグレーションが可能となっている。)

# 2.2.3 基板のパターン設計

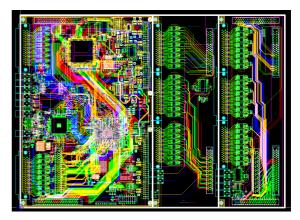

開発にあたっては基板のパターン設計も行い、パターン図を作成した。その結果を図5に示す。

基板上では 500MHz 以上の高速な信号が伝送されるので、信号波形を崩さずに伝送するにはインピーダンスミスマッチングによる信号の反射を抑える必要がある。また、内部クロックによるプログマブルデバイス間の同期や A/D コンバータのデータバスのスキューを調整する必要性から、パターン上に伝送される信号の伝搬遅延をある程度正確に調整する必要がある。

| 0x0000000 | SRAM          |

|-----------|---------------|

| 0x01FFFFF | SKI           |

| 0x0200000 |               |

| 0x03FFFFF | FlashMemory   |

|           |               |

| 0x0400000 | LVDS I/O      |

| 0x040001F | EVDS I/O      |

|           | 2777.710      |

| 0x0400020 | NIM I/O       |

| 0x0400021 | LVTTL I/O     |

| 0x0400022 |               |

|           | LED           |

| 0x0400023 |               |

| 0x0400024 |               |

|           | モジュール内各フラグ設定用 |

| 0x040002F |               |

| 0x0400030 |               |

|           | ADC Databus   |

| 0x040003F |               |

| 0x0400040 |               |

|           | ユーザー定義用       |

| 0x3FFFFFF |               |

図 3: モジュールの VMEbus 上のアドレス空間のデフォルト値(本モジュールはデフォルトの状態では、上の図の様にアドレス空間を規定した。)

図 4:ROM データ不良によるコンフィグ失敗回避 (FlashMemory の B 領域にはあらかじめ正常なデータを格納しておき、新規に開発した回路は A 領域に格納することで A 領域のデータに欠陥がありハングアップ場合は自動で B 領域から再コンフィグレーションするように構成されている。)

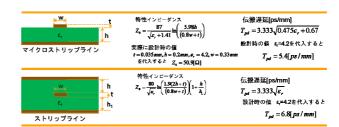

基板上で特性インピーダンスや伝搬遅延を調整するには、配線パターンをマイクロストリップラインまたはストリップラインにする必要がある。これらの配線パターンを構成するため、表層以外にも内部に複数の銅箔パターンの層が存在する多層基板を導入した。

今回、多層基板の層数は 8 層とした。これは基板上の配線パターンの特性インピーダンスの調整を行いつつ、大量の配線を行うために最低限必要な層数である。

図 5: 基板のパターン図(各 IC 間の配線数はおよそ 7600 本。配線パターンの特性インピーダンスを調整可能な状態で全ての配線を行うために 8 層基板を利用した。)

図 6: 配線パターンの特性 ( $\epsilon$ r は基板の基材 (緑色の領域) の比誘電率。茶色の領域は銅箔を示す。基材の比誘電率は FR-4 のものを、そのほかの数値は基板製造会社の製造仕様書のものを使用して計算した。)

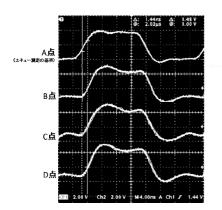

各プログラマブルデバイス間のクロックのスキューはクロックドライバ CDCVF2505 の出力間のスキュー100ps、ジッタ 400ps [7]と合わせて 1ns 以内に収まるよう各配線の長さの許容差を 30mm 以内とした。

また、A/D コンバータのデータバスは FPGA と直接接続されており、FPGA のセットアップ時間とホールド時間を考慮してデータバス上の信号がFPGA に到達するタイミングを調整する必要がある。A/D コンバータのデータバスのスキューとジッタそして基板製造時の銅箔の厚みや基材の寸法のバラツキを考慮して、設計配線長の差のみで生じるスキューを計算上±50ps 以内に収まるように配線パターン長を定めた。

#### 3. モジュールのテスト

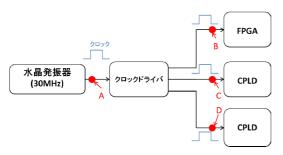

各プログラマブルデバイスには内部の水晶発振器から発生したクロックをクロックドライバ経由で分配している(図 4)。インピーダンスミスマッチングによる波形の乱れやスキューによる誤動作の恐れがないかオシロスコープで測定した。

図 7: モジュール内部のクロックの測定 (モジュール内部の水晶発振器のクロックをクロックドライバで各プログラマブルデバイスに分配している。 A での波形と A~B,A~C,A~D のスキューをオシロスコープで測定した。)

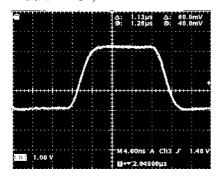

図 8: クロックの波形の測定結果 (図 7 の A 点で モジュールのクロック波形の測定結果。)

図 9: クロック間のスキューの測定結果(図 7 の A 点を基準に各プログラマブルデバイスのピン直前の点 B,C,D におけるスキューを測定した。)

測定に使用したオシロスコープは Tektronix のTDS3014Bで、クロックの波形測定には FET プローブ P6243 を使用し、スキューの測定には受動プローブ P6112 を使用した。測定の結果、クロック波形はすべてデバイスの規格を満足している、またオシロスコープで測定可能なレベルの大きなスキューはなかった。

クロックの波形・スキューの他に、電源電圧の確認、プログラマブルデバイスのコンフィグレーション、各 IC・I/O の動作確認を行い、モジュール単体

のテストでは正常に動作することが確認された。

# 4. まとめ

東北大学電子光理学研究センター次期電磁カロリ。メータシステム開発に向け、高性能 FPGA と高速フラッシュ型 A/D コンバータを搭載したマルチチャネル多目的ロジックモジュールを開発した。

本モジュールは優れた汎用性を持ち、電磁カロリメータシステムの信号処理以外にも、現在復旧作業中の電子光理学研究センター電子線形加速器トリガ系に導入する予定である。

# 参考文献

- [1] K.Nanbu, et al., Development of a Multi-Purpose Logic Module with the FPGA, Research Report of Laboratory of Nuclear Science, Vol.40 (2007), p.27

- [2] Xilinx, Virtex-5 FPGA Data Sheet:DC and Switching Characteristics, http://www.xilinx.com

- [3] National Semiconductor, ADC08D1020 Low Power 8-Bit Dual 1.0 GSPS or Single 2.0 GSPS A/D Converter, http://www.national.com

- [4] National Semiconductor, LMH6552 1.5GHz Fully Differential Amplifier, http://www.national.com

- [5] Texas Instruments, CDCE421A Fully-Integrated Wide Range Low-JitterCrystal Oscillator Clock Generator, http://focus.tij.co.jp

- [6] VME MEMBER, VMEbus アーキテクチャ・マニュアル Revision C.1

- [7] Texas Instruments, CDCVF2505 3.3-V CLOCK PHASE-LOCK LOOP CLOCK DRIVER, http://focus.tij.co.jp