# Reliable Control System For Future Particle Accelerators

# DRAFT 14/09/2009

Artem Kazakov

Department of Accelerator Science School of High Energy Accelerator Science The Graduate University for Advanced Studies

2009

# **Table of Contents**

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1 Control Systems overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                  |

| 1.1 The "standard model" of accelerator control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

| 2 Improving the control system reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                    |

| 2.1 Reliability Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

| 2.2 Reliability of a particle accelerator and control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14                                                                                                 |

| 2.3 Components of the CS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                    |

| 2.3.1 Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                 |

| 2.3.2 Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                                                 |

| 2.3.3 People                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                    |

| 2.3.4 Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

| 3 EPICS Redundant IOC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                                                 |

| 3.1 Experimental Physics and Industrial Control System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                                                 |

| 3.2 Redundant IOC introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

| 3.3 Redundant IOC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

| 3.3.1 Hardware Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                    |

| 3.3.2 Software Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

| 3.3.3 RMT API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 3.4 Redundant IOC generalization: bringing RIOC to other architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

| 3.4.1 Porting process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                    |

| 3.4.2 Results and performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

| 3.4.3 Failover Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                    |

| 3.4.4 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

| 4 redundant Channel Access Gateway                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

| 4.1 Channel Access Gateway description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

| 4.1.1 Channel Access Gateway operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39                                                                                                 |

| <ul><li>4.1.1 Channel Access Gateway operation</li><li>4.1.2 Channel Access Gateway -&gt; single point of failure!</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39<br>39                                                                                           |

| <ul> <li>4.1.1 Channel Access Gateway operation</li> <li>4.1.2 Channel Access Gateway -&gt; single point of failure!</li> <li>4.2 Redundancy without load-balancing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39<br>39<br>41                                                                                     |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>39<br>41<br>41                                                                               |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>39<br>41<br>41<br>44                                                                         |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>39<br>41<br>41<br>44<br>44                                                                   |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>44                                                                   |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>44                                                                   |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>44<br>45<br>47                                                       |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>45<br>47<br>49                                                       |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>44<br>44<br>44<br>45<br>47<br><b>49</b><br>49                                          |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>45<br>47<br><b>49</b><br>49<br>49                                    |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>45<br>47<br><b>49</b><br>49<br>49<br>52                              |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>41<br>41<br>44<br>44<br>45<br>47<br><b>49</b><br>49<br>52<br>52<br>53<br>54                  |

| <ul> <li>4.1.1 Channel Access Gateway operation</li> <li>4.1.2 Channel Access Gateway -&gt; single point of failure!</li> <li>4.2 Redundancy without load-balancing</li> <li>4.2.1 Redundant Channel Access Gateway Architecture.</li> <li>4.2.2 General Purpose External Command Driver for RMT</li> <li>4.2.3 Redundant Channel Access Gateway Implementation summary</li> <li>4.3 Redundancy with load-balancing</li> <li>4.3.1 Conclusion.</li> </ul> 5 Redundant IOC on Advanced Telecommunication Computing Architecture: Reliable software + Reliable hardware <ul> <li>5.1 Advanced Telecom Computing Architecture (ATCA).</li> <li>5.2 SAF Specifications.</li> <li>5.2.1 Service Availability forum.</li> <li>5.2.2 Hardware Platform Interface (HPI)</li> <li>5.2.3 Application Interface Specification (AIS)</li> <li>5.3 Redundant IOC on ATCA.</li> </ul> | 39<br>41<br>41<br>44<br>44<br>45<br>47<br><b>49</b><br>49<br>49<br>49<br>52<br>53<br>54<br>54      |

| <ul> <li>4.1.1 Channel Access Gateway operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

| <ul> <li>4.1.1 Channel Access Gateway operation</li> <li>4.1.2 Channel Access Gateway -&gt; single point of failure!</li> <li>4.2 Redundancy without load-balancing</li> <li>4.2.1 Redundant Channel Access Gateway Architecture.</li> <li>4.2.2 General Purpose External Command Driver for RMT</li> <li>4.2.3 Redundant Channel Access Gateway Implementation summary</li> <li>4.3 Redundancy with load-balancing</li> <li>4.3.1 Conclusion.</li> </ul> 5 Redundant IOC on Advanced Telecommunication Computing Architecture: Reliable software + Reliable hardware <ul> <li>5.1 Advanced Telecom Computing Architecture (ATCA).</li> <li>5.2 SAF Specifications.</li> <li>5.2.1 Service Availability forum.</li> <li>5.2.2 Hardware Platform Interface (HPI)</li> <li>5.3 Redundant IOC on ATCA.</li> </ul>                                                          | 39<br>41<br>41<br>44<br>44<br>45<br>47<br>49<br>49<br>49<br>49<br>49<br>52<br>53<br>54<br>54<br>57 |

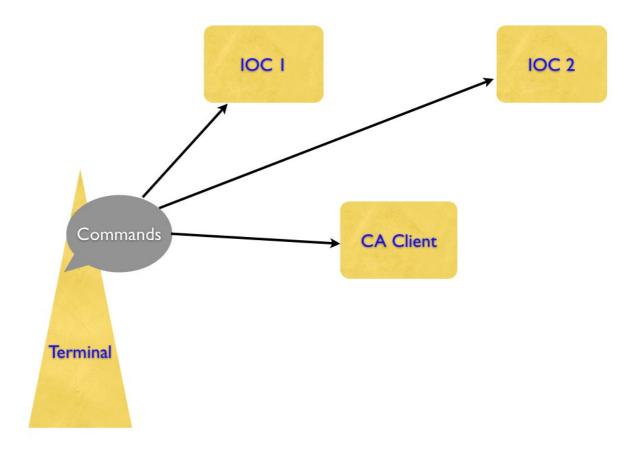

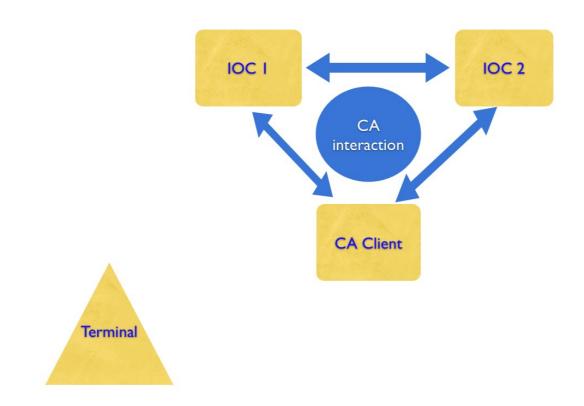

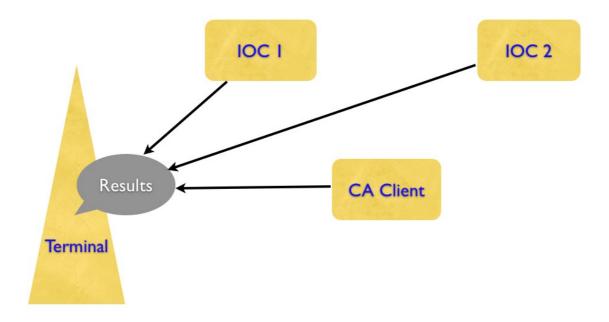

| 6.1.1.1 Typical Test Scenario                                                                                                                                                                                                                       | 59 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.2 Solution: Automation                                                                                                                                                                                                                            |    |

| 6.2.1 EPICS Test Automation Package Architecture                                                                                                                                                                                                    |    |

| 6.2.1.1 Cfg module                                                                                                                                                                                                                                  |    |

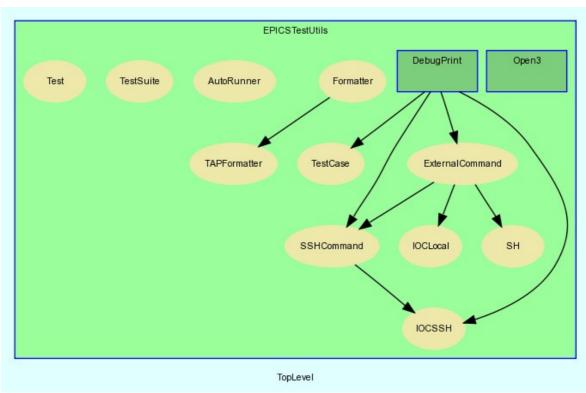

| 6.2.1.2 EPICSTestUtilModule                                                                                                                                                                                                                         | 67 |

| 6.2.2 Conclusion                                                                                                                                                                                                                                    | 71 |

| 7 Conclusion and summary of the results                                                                                                                                                                                                             | 72 |

| Acknowledgments                                                                                                                                                                                                                                     |    |

| Reference List                                                                                                                                                                                                                                      |    |

| Illustration Index                                                                                                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                     |    |

| A. Appendix                                                                                                                                                                                                                                         |    |

| A. Appendix<br>A.I. Files                                                                                                                                                                                                                           |    |

|                                                                                                                                                                                                                                                     |    |

| A.I. Files<br>A.II. Building RIOC                                                                                                                                                                                                                   |    |

| A.I. Files                                                                                                                                                                                                                                          |    |

| <ul><li>A.I. Files</li><li>A.II. Building RIOC</li><li>A.III. Building load-balancing redundant CA gateway</li></ul>                                                                                                                                |    |

| <ul><li>A.I. Files</li><li>A.II. Building RIOC</li><li>A.III. Building load-balancing redundant CA gateway</li><li>A.IV. Ca gateway implementation notes.</li></ul>                                                                                 |    |

| <ul> <li>A.I. Files</li> <li>A.II. Building RIOC</li> <li>A.III. Building load-balancing redundant CA gateway</li> <li>A.IV. Ca gateway implementation notes</li> <li>Step 1: Redundancy without Load-Balancing</li> </ul>                          |    |

| <ul> <li>A.I. Files</li> <li>A.II. Building RIOC</li> <li>A.III. Building load-balancing redundant CA gateway</li> <li>A.IV. Ca gateway implementation notes</li> <li>Step 1: Redundancy without Load-Balancing</li> <li>rmtScriptDriver</li> </ul> |    |

### Introduction

Modern particle accelerator machines are complex and large scale structures. Large projects like Large Hadron Collider and International Linear Collider (ILC) consist of thousands of components that are spread over big distances in underground tunnels[1]. Machines of that scale and complexity raise a set of challenges for all subsystems of the accelerator. With constantly growing size and complexity of particle accelerators the role of the control system becomes more and more important for a successful operation. One of the biggest concerns for large machines is availability. Because of a huge number of components, even very reliable components, final availability of the accelerator might suffer of continuos failures in one of the subsystems.

| Availability | Downtime Per Year |

|--------------|-------------------|

| 90%          | 36.5 days         |

| 99%          | 3.7 days          |

| 99.9%        | 9 hours           |

| 99.99%       | 53 min            |

| 99.999%      | 5 min             |

| 99.9999%     | 32 sec            |

### Table 1. Availability and downtime per year

For example target availability for the International Linear Collider is 75%[1], but in order to achieve that, the control system has to be available for 99-99.9% of time (15 hours of down time is "allocated" for the control system of the ILC. See Table 1). Design draft specifies that the ILC control system will consist from ~1200 "crates", and that translates into 99.999% availability for each crate. Such availability has not been a requirement for present accelerator control systems. Therefore it sets a new challenge for control system designers, implementors and operators. A multilevel systematic approach should be taken in order to achieve these availability goals.

Lets analyze availability indicators for current accelerators. Typical high energy physics accelerator currently has an availability of 75-85%[2]. Though there are some examples of much better availability: Pohang Light Source (2008) - 97% (with controls responsible for 2% of downtime)[3]; SOLEIL light source (2007) - 95.7% (with controls responsible for 2.7% of downtime)[4]; KEK Linac (2008) - 98.3% (with controls responsible for 13.3% of downtime)[5]. For KEK Linac it means that control system availability was around 99.76%. The KEK Linac control system consists of 30 VME crates, 150 PLCs, 30VXI, 15 CAMAC, 24 intelligent oscilloscopes[6]. ILC control system is 1195 ATCA crates, 8356 network switches and thousands of other lower level control components. ILC control system has 10 ~ 100 times more components than KEK Linac control system. Such tremendous increase in a number of components will dramatically reduce the availability indicators for the control system. Therefore availability issues have to be seriously considered for the future particle accelerator control systems. This research was devoted to that particular goal.

The first chapter provides some introductory information regarding accelerator control systems, historical overview of the control system evolution and a modern view on building control systems.

The second chapter of this work describes different approaches to improve availability of a particle accelerator. The general reliability theory is briefly introduced. Then the applications of that theory to accelerator control system are discussed. An accelerator control system can be roughly separated into four major parts: hardware, software, humans and procedures. Analysis is done for each of these four components. Each of these parts requires different approaches in order to achieve high availability. This work covers improvement of the software and hardware components. Hardware reliability is improved through implementation of redundancy, and software reliability is improved through implementation on how these goals are met.

Chapters 3,4,5 describe my contribution to improve reliability of accelerator control system. This work is mostly concentrated on improvement of software and hardware components using EPICS software. EPICS stands for Experimental Physics and Industrial Control System. It has

more than 15 years history of usage and has been being developed during all these years. It is widely used in many accelerator laboratories all over the world, including KEK, where it is a basis for the KEKB control system[7].

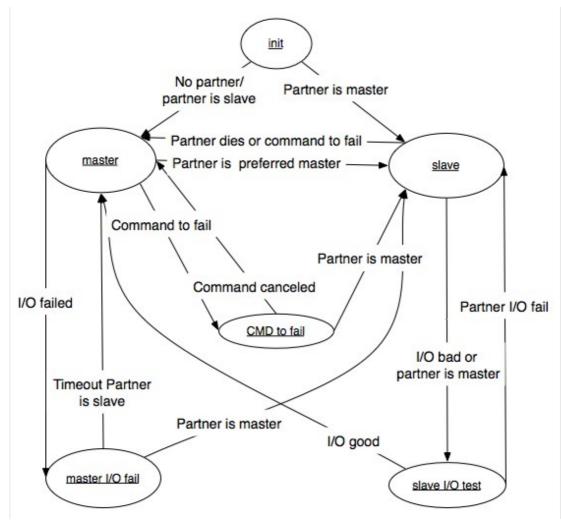

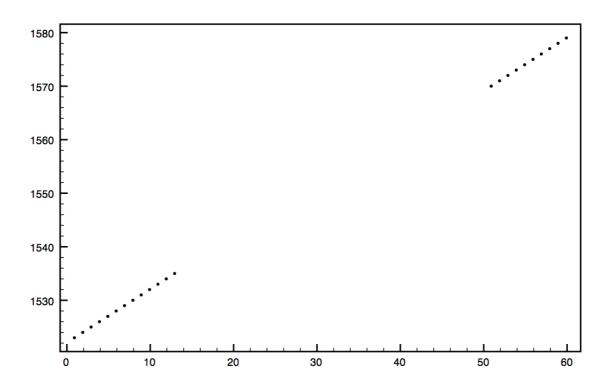

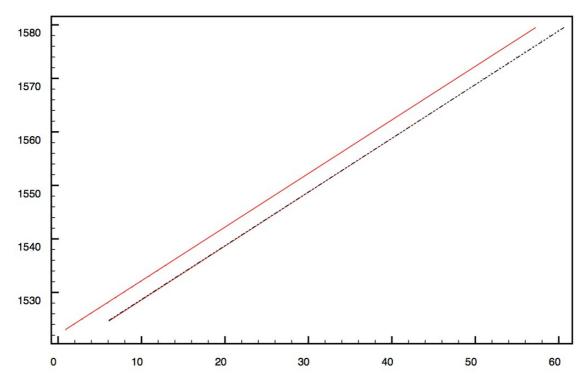

Chapter 3 describes the EPICS redundant IOC. In order to achieve high availability (such as 99.999%), redundancy is essential (as discussed in Chapter 3, section 3.1, 3.2). Redundancy allows to reduce time needed to recover from a failure to a few seconds or milliseconds, instead of hours and days. The system is not stopped because of the failure and the stand-by component starts to operate immediately after the failure is noticed. The redundancy approach is a common technique used in highly available applications (more than 99.999% availability)[8]. The original EPICS software distribution lacked redundancy support. This issue was addressed by developing EPICS redundant IOC. The initial design and development was made by DESY[9]. Unfortunately from the very beginning only vxWorks support was looked for. Later it was realized that other OS support is needed as well. As a part of my research, in collaboration with DESY, I generalized the redundant EPICS IOC to Linux, Darwin, and other operating systems[10]. The generalization was done using the Operating System Independent (OSI) library, therefore the ported version should work on any platform, where the OSI library is fully implemented. The generalized redundant IOC is an important improvement to the EPICS control system framework. Several serious software bugs were fixed in the original Redundancy software. The result of this work is a very important improvement to the existing RIOC implementation. First, it allowed to use RIOC on many operating systems, such as Linux and MAC OS X, therefore providing much wider application field for the RIOC. Second, it allowed to include the support for the RIOC into the official EPICS distribution from version 3.14.10[11]. Third, working on this project resulted in modification and splitting the original software into several libraries which can be used independently. An example of such usage is provided in the next chapter, describing the implementation of redundant and load-balancing Channel Access gateways. In chapter 6 the generalized version of the RIOC is extended to support the Advanced Telecom Computing Architecture (ATCA) platform. These projects would have been impossible without the generalization of the original RIOC and improvements done during this work. To summarize: the EPICS redundant IOC was designed and developed by DESY[9], but it was only available for

vxWorks operating system. I generalized the EPICS redundant IOC to other operating systems and made it available for wider range of applications[10]. Within this work the redundant EPICS IOC was implemented on Linux, Mac OS X and Solaris systems for the first time.

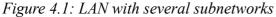

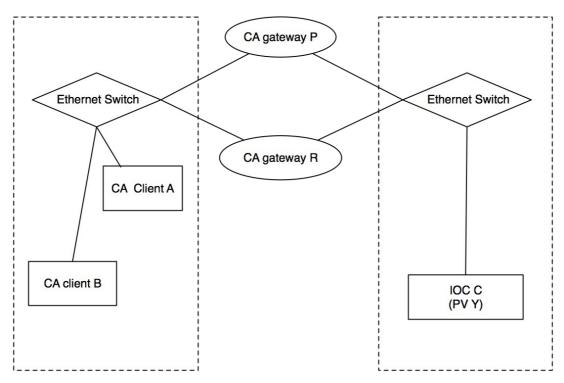

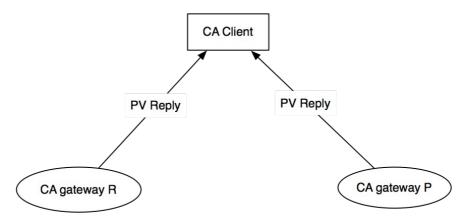

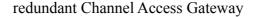

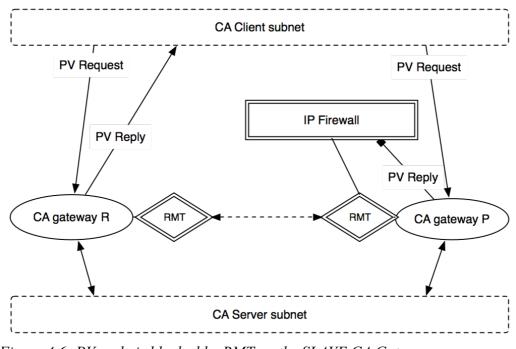

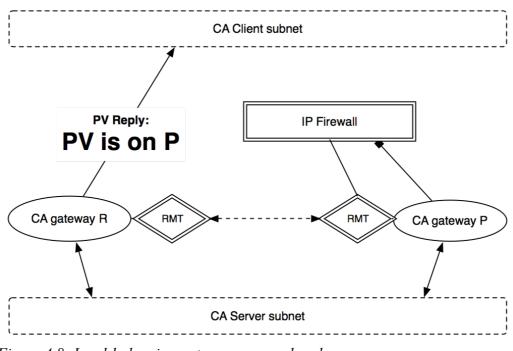

As mentioned above using the generalized versions of RIOC libraries, Channel Access Gateway was made redundant and load-balancing. This new and original development is described in Chapter 4. Channel Access gateways are in operation in many places. They allow separating control networks into several administrative subnetworks. Also they can be used as a security tool: providing restricted access to the control network, for example read-only access from public networks. Besides this administrative and security aspects gateways also optimize the number of Channel Access (CA) connections to the IOCs, because several CA clients can share one connection to an individual IOC. Due to these important functionalities gateways play a growing role in today's installations. Performance and functionality have been continuously improved over the last years. The availability of this service is key for machine operations in many places. This was the driving force to implement redundancy also for the CA gateways[12]. The Channel Access gateway originated at APS by during the years has been developed by Jim Kowalkowski. Further development was done by several people at APS, LANL and BESSY[13]. I implemented the redundant and load-balancing Channel Access gateway, based on the original Channel Access Gateway.

The redundant and load-balancing Channel Access Gateways were implemented within this research. The development was done using the generalized version of RIOC libraries discussed in the chapter 3. The implementation of the redundant CA gateway allowed to escape the single-point of failure, and by introducing the load-balancing the performance and throughput was improved in the number of 2. Load-balancing version of the CA gateway brings availability improvements as well, due to the fact that half of the connections are handled via the secondary gateway, these connections will not be affected when the failure occurs on the primary gateway.

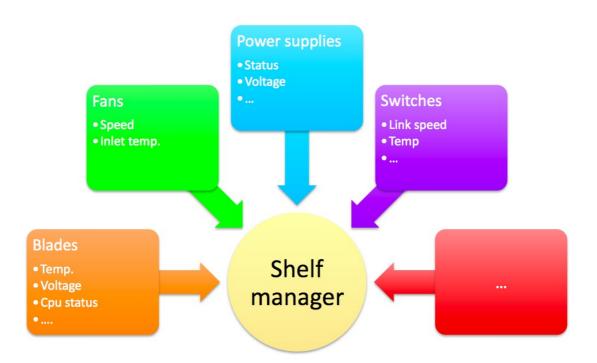

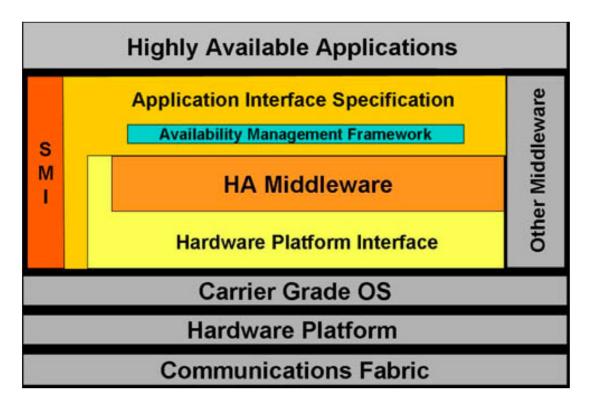

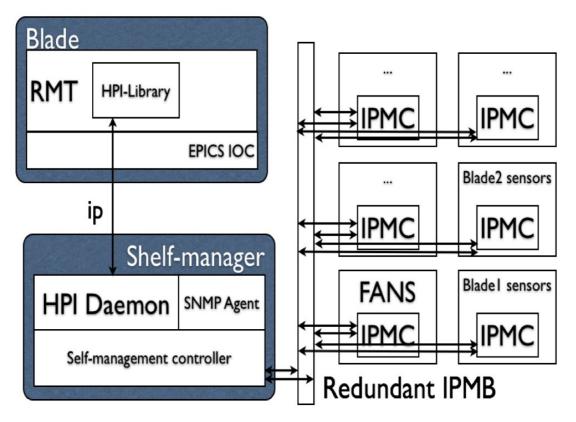

In chapter 5 new hardware standard ATCA and its application to control system are described. Within this research a support for Advanced Telecommunication Computing Architecture (ATCA) was added to the RIOC software. This addition, called ATCA-driver, allows to monitor the ATCA-hardware and provide better availability. This driver can help predict hardware failures and allows to decrease the Channel Access clients reconnect time from 30 to 2 seconds.

Using reliable software in conjunction with reliable hardware can give us even more reliable solutions. Recently Advanced Telecommunication Computing Architecture standard is gaining attention in High Energy Accelerator field as platform for modern controls and Data Acquisition (DAQ) systems. ATCA is an open standard developed by consortium of telecom vendors and users; and from its very early days it is aimed to high reliability, high bandwidth and modularity. Nowadays it is widely used in telecom industry and is widely supported by many big vendors. The ILC control system requirement for a single control shelf is 99.999%. ATCA hardware available on the market provides this level of availability or better, therefore ATCA was suggested to be used in ILC control system. Even though ATCA provides redundant cpu boards, power supplies, interconnections and other facilities, redundant IO boards and software that can work with ATCA hardware and utilize its capabilities must be developed[1].

For the reasons mentioned above I developed a driver for the Redundant EPICS IOC (RIOC) which provides support for ATCA. Using the Hardware Platform Independent library (HPI) it allows the RIOC to monitor the status of the hardware it's running on. Using this information, fail-over decisions can be made even before the "real" failure happens. For example, if the temperature starts to rise there is some delay until system crashes because of overheating. During that time the fail-over sequence can be triggered. Therefore the fail-over happens in a more stable and controlled environment. An obvious and very important benefit is that client connections can be gracefully closed and clients would reconnect to the stand-by IOC within 2 seconds. In case of a real hardware failure it would take up to 30 seconds (default Channel Access timeout).

This ATCA RIOC driver can be also utilized on any computer which has an HPI support. Therefore providing increased availability for the platforms other than ATCA. For example modern computer severs are usually equipped with the temperature, voltage etc. monitoring hardware. OpenHPI distribution of HPI supports such hardware on Linux operating system[14]. The ATCA and HPI library are designed and created by other people. The ATCA RIOC driver was developed by me.

Chapter 6 presents another approach to improve the reliability - by means of improving the quality of the software. An important part of this process is the software testing and quality assurance. In early years EPICS supported only one operating system for the server side - vxWorks, and one operating system for the client side - Sun OS; and it was well tested at

Argonne National Laboratory. But in recent years EPICS has gained support for many operating systems and hardware platforms and now it supports more than 10 operating systems[15]. Each institution uses its own collection of OS+EPICS running on different hardware. Most of these combinations are not very well tested, due to a lack of convenient, easy to use and reliable system integration testing mechanism. Therefore it leads to a potentially dangerous situation when an untested and unproved software is used for the operation. Obviously a decent automated test system is needed for EPICS software distribution[16].

EPICS has a decent unit-test system included in the base distribution. It has been continuously extended by core-developers as EPICS evolve and new features have been added. Basically a unit-testing is a testing of small pieces (functions) of code, to check that they perform correctly. But it does not mean that these pieces would work when combined together. For that purpose there is another test package, which consists of system tests, when real IOC's are installed on distributed machines and then it is checked if these systems perform correctly altogether. The unit tests and the system test software was developed by EPICS community. I designed and developed the original software for automating the system test procedure.

Originally that system test package for EPICS consisted of several programs/IOCs and text file instructions how to run them. But it is not convenient and takes a lot of time for developers and users to understand how to run these tests, prepare different machines, upload, configure and start the IOCs, preform a test and compare the results. As a part of my research I have developed a system that automates the process of a system testing and system integration testing, and provides a flexible environment to create these tests. This newly developed software supports a wide variety of configurations by default and can be easily configured using simple configuration file. It is developed in the high-level object oriented scripting language Ruby, which makes it easy to extend and add new functionality. Usage of this automated test systems greatly simplifies the testing process. It allows to run a predefined set of tests on a predefined set of computers in a fully automated manner. It requires to create a configuration file, specifying the computers and corresponding test that must be performed. Then only one command must be issued by human to run all the tests. If compared to manual testing, it saves tremendous amount of human time and effort. Due to automation chances for human error are greatly reduced too. After all tests are executed the system provides a detailed report.

6

Nowadays, a control system of a particle accelerator is a very important subsystem playing a significant role in operation of the machine. But it was not always like that. First particle accelerators did not have any computerized control system and were operated using analogue devices and interfaces. When the computer industry developed enough, relatively cheap and powerful computers became available in the late sixties. As computers became affordable for physics laboratories, physicists started to experiment with the new possibilities that computers provided. This was the beginning of the computerized control system era for particle accelerators. Since its conception a computerized control system evolved through the following periods:

- non-centralized computer adjuncts to the accelerator

- centralized computer control, vendor-oriented, with very substantial custom solutions (example PDP-10, shown on Figure 1.1)

- distributed networked computer control, standards oriented, with mostly commercial solutions

Figure 1.1: PDP-10 the centralized control system.

These eras are not, however, mutually exclusive; even today systems characteristic of the earliest period can still be found, even at the newest accelerators. Of course, interwoven through these periods is the history of the computer industry itself, from mainframe computers to minicomputers, to workstations, to personal computers, to commodity single board computers. Today, accelerator operators and physicists assume that a powerful computer control system should be part of an accelerator. The success of a controls group in delivering high capability controls solutions that are transparent and user friendly is a major component of what a controls system can contribute to the successful operation of a facility. Another important role of an accelerator control system is to provide a tool which allows the scientists to implement their ideas and theories in hardware. For that purpose an accelerator control system must provide flexible tuning capabilities, different abstraction layers and simulation capacity[17].

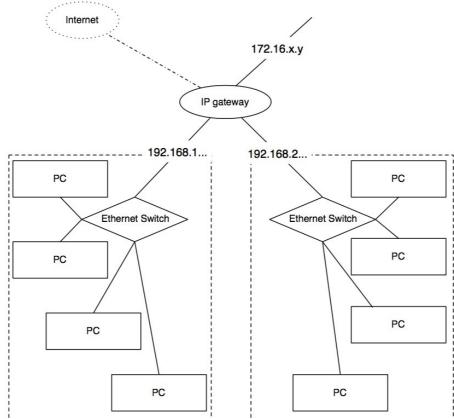

Most modern particle accelerators control systems are distributed computer systems, built on open standards. Current trend is to use more "commercially of the shelf" available components and solutions. The distributed control system provides a great flexibility, computational power and scalability; on the other hand it is more complex than the centralized model and raises a lot of challenges for the designers, implementors and maintainers. Some of those problems rise from the distributed nature of the system. Along with a greater scalability the problem of the reliability rises. Even if the most reliable components are used, when we combine thousands of these components the probability of a failure rises drastically. Another issue emerges from the physical distribution over a large space, often not easily accessible for the service and maintenance, and those factors play an important role in the system reliability. Therefore distributed systems require a careful design if the high reliability is sought. Overall reliability constrains and maintenance requirements for an accelerator control system are more strict than for the other accelerator subsystems. Normally during the year there are one or more maintenance periods during which most of the subsystems are stopped. Nevertheless the control system is often needed to be operational even during these maintenance periods in order to do the maintenance of the other subsystems. Therefore when the control system is designed these considerations should be taken into account.

# 1.1 The "standard model" of accelerator control system

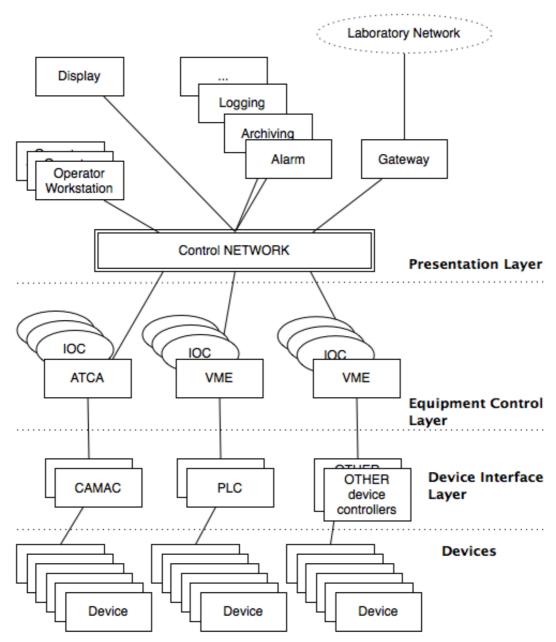

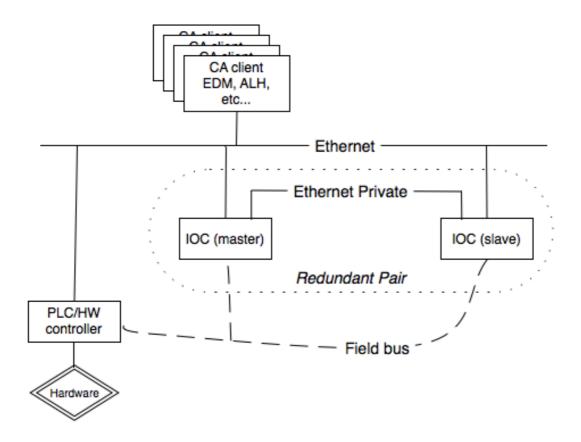

Figure 1.2: The standard model of a control system.

Most modern distributed accelerator control systems incorporate so called "Standard model" for the accelerator control system (Figure 1.2). The standard model defines three layers of abstraction of the controlled equipment:

- Presentation Layer

- Equipment control Layer

- Device Interface Layer

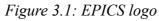

The highest level of abstraction is the Presentation Layer, includes operator consoles, simulation systems, archives, log managers, alarm handling and other components. The operations software runs at this level. An example of Presentation Layer can be seen on Figure 1.3.

Figure 1.3: Presentation layer - operator consoles in KEKB control room

Figure 1.4: MVME5500 cpu board

The Equipment control Layer consists of Input Output Controllers (IOC), that are connected to the device controllers via different fields buses, which belong to device interface layer. Typically these IOC controllers are VME cpu boards (Figure 1.4), running real-time operating system like vxWorks, or general purpose operating system like Linux. An example of such system representing the Equipment Control Layer is shown on Figure 1.5. It worth noting that modern developments in embedded technology allows to run IOC and device controller on the same chip. That makes Device Interface Layer and Equipment Control Layers indistinguishable.

Figure 1.5: Device control layer - VME crates

There are two schemes for designing accelerator control system of the standard model. One is to develop nearly all of the software by themselves, for example, SRRC (Synchrotron Radiation Research Center) in Hsinchu, Taiwan. In the past it was common practice to develop in-house control systems. The other is to make use of professional toolkits, for example, business software SCADA or use one of the available controls software developed specifically for physics experiments, such as EPICS, TANGO, DOOCS and many others. In recent years this approach is common, laboratories and organizations all over the world prefer to collaborate and synergize their efforts on development of common control system software. This approach proved to be very successful[15].

### 2.1 Reliability Basics

There are several possible definitions of reliability and availability. Common definition of availability as a measure of the ultimate uptime is shown in Equation 2.1:

$$availability = \frac{uptime}{uptime + downtime}$$

where *uptime* is the time the system is required to provide its function, and *downtime* is the time the system was not available for operation due to failures or unplanned maintenance. The classic definition of reliability is the probability that a person of system will perform required function under stated conditions for a specified period of time. Therefore time is an essential part of the reliability definition and expected uptime, repair and maintenance times, idle times and unplanned occurrences all affect the measurement of a reliable system.

Repair and maintenance times are necessary to provide a reliable system over a long period of time.

Idle time is defined as time that a system could be providing the required function, but is not. In an accelerator system, this would include times that beam is available, but is not being delivered to a user. Scheduling problems, experimental set ups, other equipment failures can all cause idle time.

Unplanned occurrences will always be a part of complex systems such as accelerators. While they are hard to plan for, they do have to be accounted for in the reliability equation. Power outages, failure of equipment, even weather can cause a system to be unreliable.

We also should take into account that reliability is highly dependent on the type of the desired operation more. If it is short time operation with long maintenance and repair time then it is pretty easy to keep the reliability high. If, however the operation is required for long periods of

uninterrupted service with little time of maintenance and repair, reliability will suffer. The simplest representation of availability in terms of reliability parameters MTBF and MTTR is shown in Equation 2.2.

$availability = \frac{MTBF}{MTBF + MTTR}$

### Equation 2.2

Where MTBF - mean time between failures and MTTR - mean time to repair. And as can bee seen from that equation, general approach to improve the reliability of any system would be to increase MTBF and to decrease MTTR. For highly available systems (99.999% and better) the redundancy becomes essential, because of the non-zero MTTR value. Redundant implementation provides a hot stand-by component, which replaces the failing one as soon as failure is noticed. Redundant systems allow to reduce MTTR to seconds or milliseconds, instead of hours or days in a non redundant system.

Careful monitoring and logging is important in order to achieve high availability. Hardware has a finite lifetime and it in terms of reliability it passes different stages within this lifetime. As it can be seen from the figure there are "burn-in", normal, and "wear-off" periods. It is crucial to understand where you are on this graph in order to maintain the desired level of availability and properly interpret the data, it is good to remember that it is common for reliability assumptions to presume a constant failure rate[18].

### 2.2 Reliability of a particle accelerator and control system

Particle accelerators are very complex machines and consist of thousands of components. A typical high energy physics (HEP) accelerator currently has an availability of 75-85%. With so many more components that could potentially fail, the ILC availability would be unacceptably low unless significant attention is paid to component reliability. With the increasing number of components the MTBF decreases and MTTR increases because of the increased complexity of the machine and physical distribution. The study shows that in order to achieve high 75-85% reliability for ILC project, MTBF of some components has to be improved 2-10 times [2]. Therefore reliability considerations when designing a new accelerators play very significant role.

Requirements for the ILC control system are even higher and translate into 99% availability. When we take into account that by design draft ILC control system consists from ~1200 ATCA crates we will get 99.999% availability requirement for each crate. In order to achieve this availability goals single boards running within the crate must have even higher availability of 99.9999% and better. For modern hardware and software solutions this means that Redundancy must be implemented in such places. Otherwise this high numbers of availability are impossible to reach due to long MTTR.

### 2.3 Components of the CS

Most systems can be broken into four major parts: Hardware, Software, People and Procedures[19]. Accelerator Control system can also be divided in the same manner. Each of these components has its own characteristics and must be looked at in different ways in order to maintain a reliable system.

### 2.3.1 Hardware

By *Hardware* we understand the *active hardware* components of the system. Such as computers, network devices, power supplies etc. Initially hardware device is supposed to be working and flawless. But when the time passes and under the influence of external forces and natural processes of wear and tear the device or part of it will eventually fail. Repairable devices may be repaired and put back into operation. The ones that cannot be repaired are replaced by spare units. **Thus repairing or replacement of the failing hardware component restores the system to its original not failed state.** For example, if a pump fails, replacing the pump with another similar pump will restore the system to a working state.

Proper commissioning of new equipment ("burn-in") will point out infant mortality problems and incompatibilities, while a good maintenance program can help with equipment as it ages. It is important to keep track of failures of all different components of the system and analyze that data. This will help to understand when and what subsystems reach its wear-off stage and decommission or replace such systems.

### 2.3.2 Software

Computer software, or just software is a general term used to describe a collection of computer programs that perform some tasks on a computer system.

*SOFTWARE* components do not age like hardware. The unintended results in software are there from the beginning due to poor design or implementation errors. These unintended results may be "hidden" in the system and the system may function properly for the long periods of time without any visible problem. But from time to time, when certain conditions are met the system fails. These unintended results only occur when all the conditions are met for them to occur, **therefore extensive testing is even more important for software than hardware**.

Unlike hardware, when software becomes unreliable it usually needs to be rewritten, not just replaced with another copy of the same software. All the copies of the same software contain the same errors, thus the new copy will also fail under the same conditions as the original one. In order to fix the software, the software error ("bug") has to be properly analyzed and studied so that to understand the nature of the problem and to find the design flaws in the software. Therefore it is very important to keep detailed operation log of the system and running software. This information is essential when it needs to recreate the critical conditions in the synthetic environment, either to find the bug, or to make sure that the new version of the software works properly under these conditions.

### 2.3.3 People

### People make mistakes....

No matter how good a person is good at their job, they will make mistakes from time to time. That is human nature. And the goal of reliability engineering for people is to take that nature into account. Proper training and good working environment are important considerations in operator reliability. Human factors such as controls layout, work schedules, even something simple as picking the correct chair can affect the reliability of a system.

General considerations are simple: the environment should help an operator to perform best and to avoid simple mistakes. Interfaces should be natural and easy to use.

### 2.3.4 Procedures

A procedure is a specified series of actions or operations which have to be executed in the same manner in order to always obtain the same result under the same circumstances (for example, emergency procedures). Less precisely speaking, this word can indicate a sequence activities, tasks, steps, decisions, calculations and processes, that when undertaken in the sequence laid down produces the described result, product or outcome. A procedure usually induces a change. It is in the scientific method.

Clear and easy to follow procedures should be in place in order to achieve high availability. Failure analysis may show that some procedures are not optimal and repeatedly lead to errors. Obviously, in such case procedures have to be redesigned.

## 3.1 Experimental Physics and Industrial Control System

EPICS is a set of software tools and applications which provide a software infrastructure for use in building distributed control systems to operate devices such as Particle Accelerators, Large Experiments and major Telescopes[15]. EPICS software is a good representative of a modern accelerator control software. Even though some flaws and improvements are described in this work, compared to other available control software EPICS is a reliable and powerful software, providing great degree of flexibility and performance.

EPICS uses Client/Server and Publish/Subscribe techniques to communicate between the various computers. Most servers (called Input/Output Controllers or IOCs) perform real-world I/O and local control tasks, and publish this information to clients using the Channel Access (CA) network protocol. Figure 3.1 Shows EPICS logo which was inspired by schematic representation of Clients and Server connected via network. Clients and Servers are shown as colored boxes. CA

is specially designed for the kind of high bandwidth, soft real-time networking applications that EPICS is used for, and is one reason why it can be used to build a control system comprising hundreds of computers.

### Figure 3.2: EPICS architecture