# DIGITAL FEEDBACK SYSTEM FOR J-PARC LINAC RF SOURCE

S. Michizono<sup>#</sup>, S. Anami, S. Yamaguchi, KEK, Tsukuba, Japan T. Kobayashi, JAERI, Tokai, Japan

Abstract

At the proton linac of J-PARC (Japan Proton Accelerator Research Complex), an accelerating electric field stability of  $\pm 1\%$  in amplitude and  $\pm 1^{\circ}$  in phase is required for the RF system. In order to accomplish these requirements, a digital feedback system is adopted for flexibility of the feedback (FB) and feedforward (FF) algorism implementation. FPGAs are used for the real-time FB system. A DSP board is also utilized for data processing and communication between FPGAs and a crate control CPU (Host). The system was examined with the SDTL cavity, and satisfied the stability specification.

# **INTRODUCTION**

Twenty klystrons (324 MHz, 3 MW) will be installed in the J-PARC linac. An RFQ, 3 DTLs and 16 SDTL modules are driven by klystrons [1]. The maximum pulse width and repetition rate are 620  $\mu$ s, including the cavity build-up time, and 50 pps, respectively. Because the rf source should maintain the accelerating field within an amplitude stability of  $\pm 1\%$  and phase stability of  $\pm 1\%$ , a highly intelligent feedback system should be constructed. A digital feedback system using the FPGAs combined

with DSPs has been developed for these requirements. The FPGAs are in charge of fast feedback for the cavities and the DSPs will be operated for data/program exchange and a slow feedback system, such as tuning the cavities. In this report, the hardware developments and performance of the feedback system are described.

## FEEDBACK EQUIPMENT

The digital feedback system is installed in a compact PCI (cPCI crate). The backplane of the cPCI crate is specially designed so as to separate the ground line between digital and analog boards. The digital equipment, such as the CPU, DSP (Spectrum Signal Processing Inc. 'Barcelona', 4xTMS320C6701) and I/O boards, are located on left side of the cPCI crate, and analog boards, such as the RF&CLK (rf and clock generator) and Mixer&I/Q (mixers and I/Q modulators) boards, are installed on the right side. The RF&CLK board creates timing clock ( $f_{Tim}$ :12 MHz,  $f_{Trig}$ : 48MHz,  $f_{LO}$ : 312 MHz) and RF ( $f_{RF}$ : 324 MHz) signals synchronized with a distributed reference signal [2]. Since the accuracy of around 2 ps is required especially to the LO signal (312 MHz), the reference signal is planned to change from 12

\*shinichiro.michizono@kek.jp

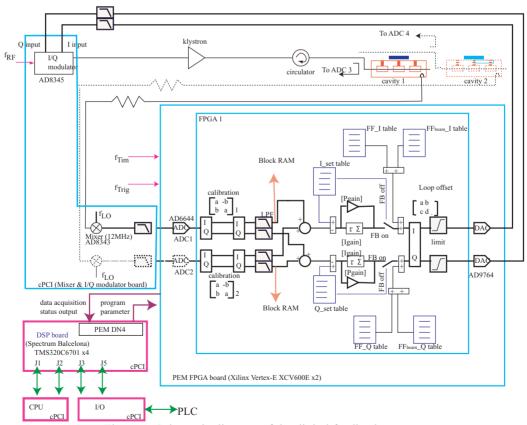

Figure 1: Schematic diagram of the digital feedback system.

MHz to 312 MHz.

An FPGA (Vertex-E XCV600E, which will be replaced by XC2V2000 in this year) sends I and Q components to an I/Q modulator (AD8345) through 14-bit DACs (AD9764). The modified signal drives a klystron. An active mixer (AD8343) receives the rf signal from the cavity and down-converts it to an IF signal (12 MHz). The FPGA obtains I/Q components by measuring the IF signals at a 48-MHz clock through a 14-bit ADC (AD6644). One of the FPGAs works for the rf signals from cavities, and another serves as a monitor of the rf signals from cavity input ports, which is used for tuner control. Figure 1 shows a schematic diagram of the digital FB system. Simple PI control is adopted for cavity control. The FF signal is added as beam compensation. The digital FB system is controlled through a PLC [3].

## FEEDBACK PERFORMANCE

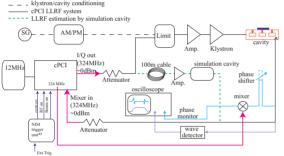

The system configuration is shown in Figure 2. Prior to a high-power test using a SDTL, a low-level FB was tested using a simulation cavity [4] with a delay line. After checking the performance with the simulation cavity,

Figure 2: Schematic diagram of the LLRF system configuration.

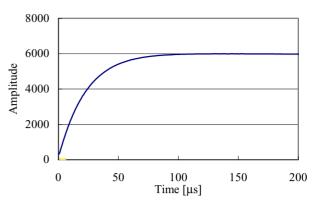

a high-power test was carried out. Figure 3 shows the step response obtained by the digital system without FB. The measured loaded Q value from this measurement was about 22,000.

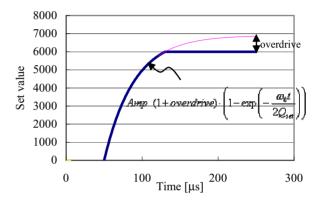

Set-values of the FB are an exponential pattern, as shown in Figure 4, for a fast build-up time with a limited

Figure 3: Step response measured by the digital system.

Figure 4: Set-values used for the feedback.

rf power. The parameters of the set-values are the amplitude, phase, overdrive and Q value for build-up ( $Q_{\text{set}}$ ). In this test, these parameters were 6,000, 0°, 5% and 40,000, respectively. This combination of amplitude and phase corresponds to 6,000 and 0 in the I and Q components, respectively.

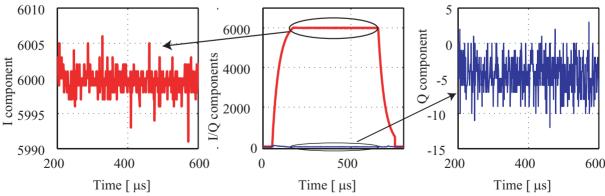

Figure 5 shows the I/Q components during FB (without FF). Proportional and integral gains of 10 and 15/1000 at a 48-MHz clock were adopted in this experiment. The variations of both components at flattop were less than 10. The corresponding errors of the amplitude and phase in the pulse were  $\pm 0.08\%$  and  $\pm 0.04^{\circ}$ , respectively. The stabilities were also evaluated using an external monitor.

Figure 5: Measured I/Q components during rf operation. Fullscale I/Q:center, expansion I: left, expansion Q: right. No feedforward was used. The proportional and integral gains for the feedback are 10 and 15/1000 at a 48-MHz clock, respectively.

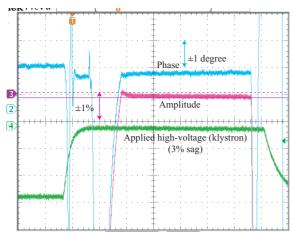

Figure 6: Waveforms of the amplitude and phase obtained by external monitors.

Figure 6 shows the amplitude and phase signals obtained with a wavedetector and a mixer, which corresponds to errors of  $\pm 0.2\%$  in amplitude and  $\pm 0.2^\circ$  in phase. The measured data with the external monitor were about 4-times larger, probably due to the ambiguity of the measurement system. Further development of the external measurement system is required for a more precise evaluation.

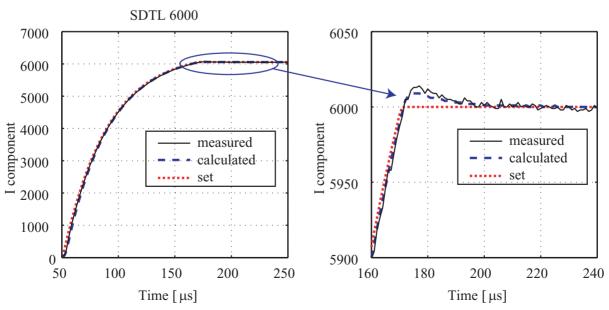

The measured values were compared with the calculated values based on the state equations. Theses showed good agreements, including the overshooting (Figure 7). This indicates that the system is well-modeled in the simulation, and that simulations will be helpful for developing new FB algorisms.

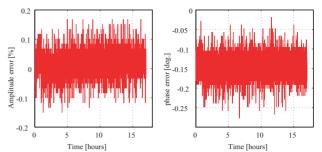

The stability of the system was also examined during long-time operation. The results are shown in Figure 8. Stabilities of  $\pm 0.2\%$  in amplitude and  $\pm 0.25^{\circ}$  in phase were achieved for more than 17 hours.

Figure 8: Trend-graphs of the amplitude and phase stabilities.

#### **SUMMARY**

A digital FB system used at the rf sources in the J-PARC linac has been developed. The requirements for the LLRF system are stabilities of  $\pm 1\%$  in amplitude and  $\pm 1^\circ$  in phase. The system was examined by a SDTL cavity, and show good stabilities of  $\pm 0.08\%$  in amplitude and  $\pm 0.04^\circ$  in phase. The stabilities remained for more than 15 hours at  $\pm 0.2\%$  in amplitude and  $\pm 0.25^\circ$  in phase.

### REFERENCES

- [1] S.Yamaguchi et al., "Overview of The RF System for The JAERI/KEK High-Intensity Proton Linac", LINAC2002, Gyeongju, Aug. 2002, p.452.

- [2] T.Kobayashi et al., "RF Reference Distribution System for J-PARC Linac", this conference.

- [3] S. Anami et al., "Control of the Low Level RF System for the J-Parc Linac", this conference.

- [4] S. Michizono et al., "Digital RF Control System for 400-MeV Proton Linac of JAERI/KEK Joint Project" LINAC2002, Gyeongju, Aug. 2002, p.184.

Figure 7: Comparison with the measured and calculated I-component. These show good agreements, including overshoot.